FPGA中值滤波实现并Modelsim仿真,与MATLAB中值滤波进行对比 |

您所在的位置:网站首页 › fpga 中值滤波 › FPGA中值滤波实现并Modelsim仿真,与MATLAB中值滤波进行对比 |

FPGA中值滤波实现并Modelsim仿真,与MATLAB中值滤波进行对比

|

文章目录

一、中值滤波算法二、FPGA实现中值滤波2.1 3*3窗口的生成2.2 排序模块2.3中值滤波模块2.4 整体RTL图

三、modeslim仿真四、matlab中值滤波五、效果对比

一、中值滤波算法

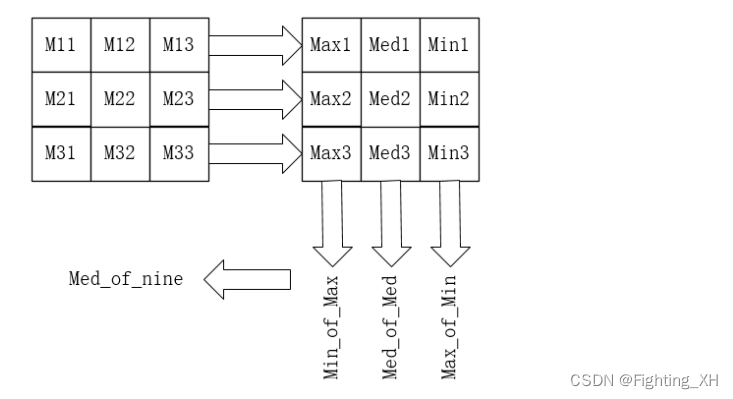

1、中值滤波算法作用 可以去除孤点噪声(适用于消除椒盐噪声(黑白噪声)),而且还可以保持图像的边缘特性,不会使图像产生显著的模糊。 2、算法原理 中值滤波算法简单来说就是:通过对33窗口中的数据进行排序,最终获得中值。 参考该博主的文章,这里不再赘述。 module filter_3x3( input clk, input rst_n, input gray_de, input [7:0] iData, output filter_de, //生成窗口花费2clk,de信号延迟两拍 output reg [7:0] oData_11, oData_12, oData_13, output reg [7:0] oData_21, oData_22, oData_23, output reg [7:0] oData_31, oData_32, oData_33 ); endmodule 2.2 排序模块FPGA中无排序IP核,因此编写如下模块,每次排序直接例化调用即可。 sort模块: module sort( input clk, input rst_n, input [7:0] data1, input [7:0] data2, input [7:0] data3, output reg [7:0] max, output reg [7:0] mid, output reg [7:0] min ); //最大值 always @(posedge clk or negedge rst_n) begin if(!rst_n) max = data2 && data1 >= data3) max = data1 && data2 >= data3) max |

【本文地址】

今日新闻 |

推荐新闻 |

对于待处理的像素,我们选择一个33的窗口模板,该窗口内的像素为待处理像素的邻近像素,对窗口内的像素分别按行列排序,最终计算出中值,用该中值代替原像素值,实现中值滤波。

对于待处理的像素,我们选择一个33的窗口模板,该窗口内的像素为待处理像素的邻近像素,对窗口内的像素分别按行列排序,最终计算出中值,用该中值代替原像素值,实现中值滤波。